CLA(carry look ahead adder)는 carry를 미리 보는 가산기인 ripple carry adder를 어떻게 하면 더 효율적으로 바꿀 수 있는가에 대한 고민에서 탄생한 회로이다.

n-bits RCA는 full adder를 n개 연결시켜 만드는 가산기인데 여기서 n이 커질수록 full adder 연결사이에서 delay가 발생하게 되어 연산속도가 더 느려진다.

Ripple이라는 단어의 뜻 그대로 carry 값이 아랫자리 수부터 파동 치며 올라와 마지막 full-adder의 Cin으로 값이 들어와야만 carry 값이 구해지므로 시간 낭비가 발생하게 된다.

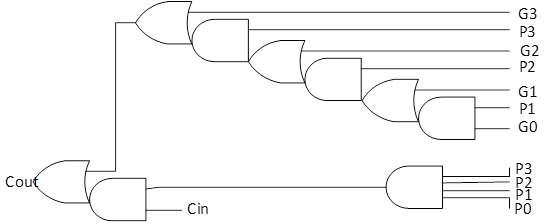

CLA는 generate와 propagate 두가지의 신호로 이루어져 있고, Gi = Ai * Bi , Pi = Ai + Bi 로 정의할 수 있다. G와 P를 통해 carry를 앞서 보고 계산할 수 있다.

Ci = AiBi + (Ai+Bi)Ci = Gi + PiCi 로 나타낼 수 있다.

<4-bit CLA Carry boolean equation>

C1=G0+P0Cin

C2=G1+P1G0+P1P0Cin

C3=G2+P2G1+P2P1G0+P2P1P0Cin

Cout=G3+P3G2+P3P2G1+P3P2P1G0+P3P2P1P0Cin

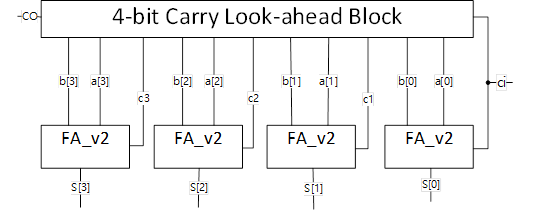

4-bit CLA를 나타낼 수 있다.

Zoom in: carry generation

32bits- CLA를 만들 때 32비트를 통째로 만들지 않고 작은 비트를 여러 개 이어 붙여서만들게 된다. CLA는 오버해드가 크기 때문에 오버헤드를 줄이기 위해 4bit CLA를 8개를 이어 붙여 만든다.

32-bits CLA와 32-bits RCA의 크기 속도 비교

CLA는 RCA가 계산이 완료될 때까지의 시간이 많이 걸리는 단점을 보완하기 위해 모든 올림수가 동시에 구해져 계산시간을 단축시키는 가산기이다. n-bits RCA는 full adder를 n개 연결시켜 만드는 가산기인데 여기서 n이 커질수록 full adder 연결사이에서 delay가 발생하게 되어 연산속도가 더 느려 진다. CLA는 Carry만 계산해주는 carry look-ahead block이 존재하면서 carry를 앞서 보면서 계산할 수 있어 속도가 빨라지게 된다.

위에서 실험에서 Fmax summary를 통해 CLA는 149.21MHz, RCA는 83.92MHz인 것을 확인한다. Fmax는 주기랑 반비례하므로 32-bits CLA와 32-bits RCA의 크기 속도를 비교할 수 있게 된다.

'디지털 논리회로' 카테고리의 다른 글

| 디지털 논리회로 / Moore FSM과 Mealy FSM의 장단점 (2) | 2021.05.03 |

|---|---|

| 디지털 논리회로 / Blocking과 non-blocking의 차이 (0) | 2021.05.03 |

| 디지털 논리회로 / carry와 overflow의 차이 (0) | 2021.05.03 |

| 디지털 논리회로 / halfadder, fulladder (0) | 2021.05.03 |

| 디지털 논리회로 / 부호가 없는 수, 2의 보수, 병렬 이진 가감산기 (0) | 2021.05.03 |

댓글